- 您现在的位置:买卖IC网 > Sheet目录369 > X28HC256SIZ-90 (Intersil)IC EEPROM 256KBIT 90NS 28SOIC

�� �

�

�

�X28HC256�

�System� Considerations�

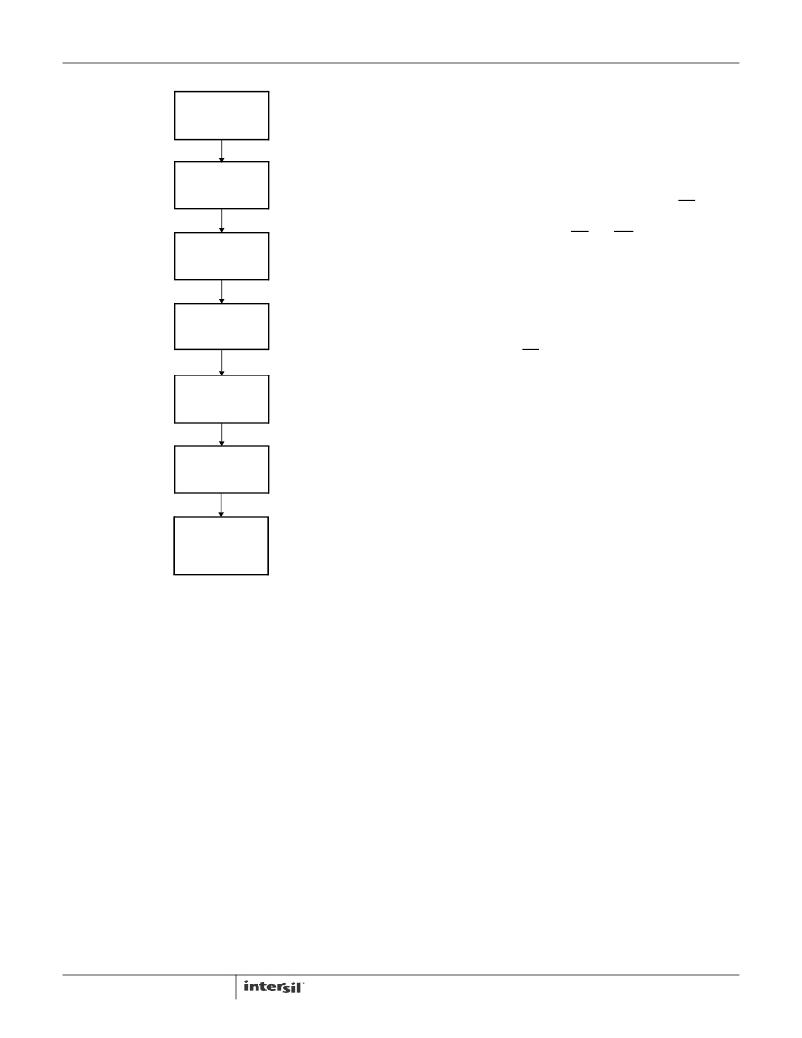

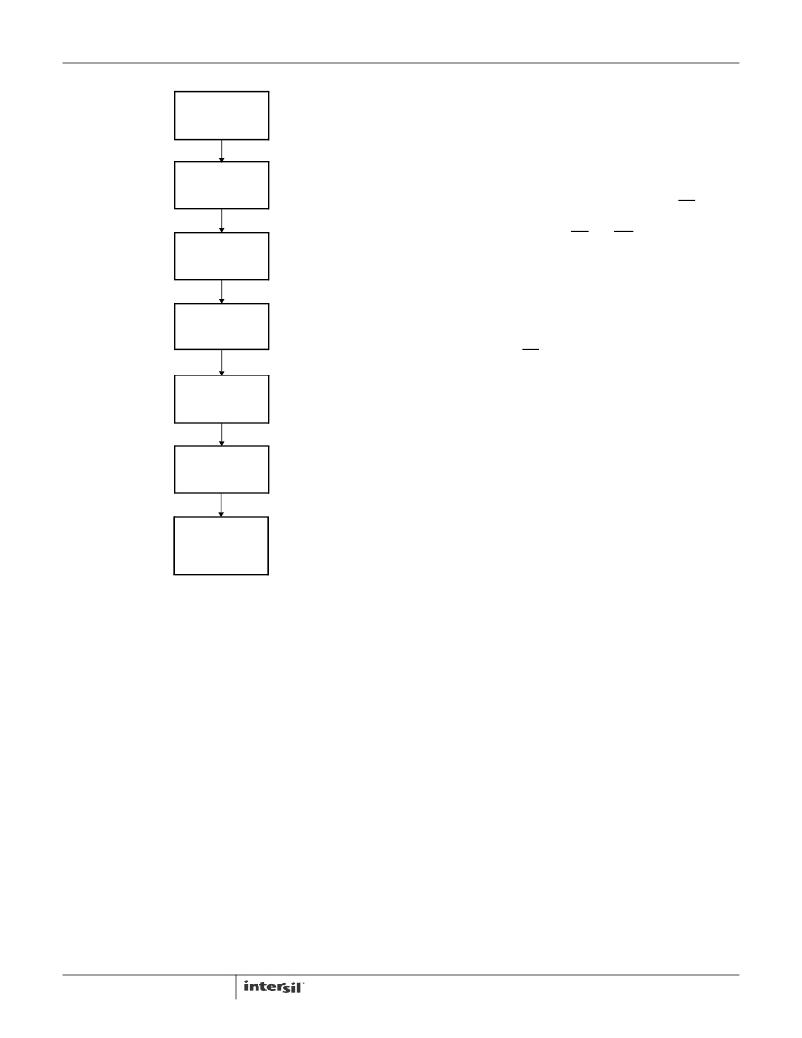

�WRITE� DATA� AA�

�TO� ADDRESS�

�5555�

�WRITE� DATA� 55�

�TO� ADDRESS�

�2AAA�

�WRITE� DATA� 80�

�TO� ADDRESS�

�5555�

�WRITE� DATA� AA�

�TO� ADDRESS�

�5555�

�WRITE� DATA� 55�

�TO� ADDRESS�

�2AAA�

�WRITE� DATA� 20�

�TO� ADDRESS�

�5555�

�AFTER� t� WC� ,�

�RE-ENTERS�

�UNPROTECTED�

�STATE�

�Because� the� X28HC256� is� frequently� used� in� large� memory�

�arrays,� it� is� provided� with� a� two� line� control� architecture� for�

�both� read� and� write� operations.� Proper� usage� can� provide�

�the� lowest� possible� power� dissipation,� and� eliminate� the�

�possibility� of� contention� where� multiple� I/O� pins� share� the�

�same� bus.�

�To� gain� the� most� benefit,� it� is� recommended� that� CE� be�

�decoded� from� the� address� bus� and� be� used� as� the� primary�

�device� selection� input.� Both� OE� and� WE� would� then� be�

�common� among� all� devices� in� the� array.� For� a� read�

�operation,� this� assures� that� all� deselected� devices� are� in�

�their� standby� mode,� and� that� only� the� selected� device(s)�

�is/are� outputting� data� on� the� bus.�

�Because� the� X28HC256� has� two� power� modes,� standby� and�

�active,� proper� decoupling� of� the� memory� array� is� of� prime�

�concern.� Enabling� CE� will� cause� transient� current� spikes.�

�The� magnitude� of� these� spikes� is� dependent� on� the� output�

�capacitive� loading� of� the� l/Os.� Therefore,� the� larger� the� array�

�sharing� a� common� bus,� the� larger� the� transient� spikes.� The�

�voltage� peaks� associated� with� the� current� transients� can� be�

�suppressed� by� the� proper� selection� and� placement� of�

�decoupling� capacitors.� As� a� minimum,� it� is� recommended� that�

�a� 0.1μF� high� frequency� ceramic� capacitor� be� used� between�

�V� CC� and� V� SS� at� each� device.� Depending� on� the� size� of� the�

�array,� the� value� of� the� capacitor� may� have� to� be� larger.�

�In� addition,� it� is� recommended� that� a� 4.7μF� electrolytic� bulk�

�capacitor� be� placed� between� V� CC� and� V� SS� for� each� eight�

�devices� employed� in� the� array.� This� bulk� capacitor� is�

�employed� to� overcome� the� voltage� droop� caused� by� the�

�inductive� effects� of� the� PC� board� traces.�

�FIGURE� 9.� WRITE� SEQUENCE� FOR� RESETTING� SOFTWARE�

�DATA� PROTECTION�

�8�

�FN8108.3�

�September� 21,� 2011�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

X28HC64JIZ-90

IC EEPROM 64KBIT 90NS 32PLCC

XCARD XK-1A

DEV KIT EVENT-DRIVEN PROC XS1-L1

XCARD XTAG-2

ADAPTER USB DEBUGGER JTAG XSYS2

XE8000EV101

EVAL BOARD FOR XE8801AMI027LF

XG4E-6431-S012

CONN PLUG 64POS 1A OPENED COVER

XLNRC

RAPID OUTPUT CONNECTOR

XLT80PT3

SOCKET TRAN ICE 80MQFP/TQFP

XRP6658EVB

EVAL BOARD FOR XRP6658

相关代理商/技术参数

X28HC256SM-12

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SM-12,

制造商:ROCHESTER 制造商全称:ROCHESTER 功能描述:LOW POWER CMOS EEPROM with hi-speed page write capability 256K EEPROM

X28HC256SM-15

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SM-70

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SM-90

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SMB-12

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SMB-15

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM

X28HC256SMB-70

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:5 Volt, Byte Alterable EEPROM